在计算机软件技术服务与硬件系统设计中,时钟源如同心脏,为整个系统提供稳定而有节奏的“脉搏”。而EMI时钟源,正是这一核心组件中兼顾高性能与低电磁干扰(EMI)的关键技术。本文将为您解析什么是EMI时钟源,并带来其最新技术动态。

什么是EMI时钟源?

EMI时钟源,全称为低电磁干扰时钟源(Low-Electromagnetic Interference Clock Source),是一种专门设计用于减少工作时产生的电磁辐射的时钟信号发生器。在计算机、通信设备、消费电子等各类电子系统中,时钟电路产生的电磁噪声可能干扰系统自身及其他附近设备的正常运行,导致数据错误、性能下降或合规测试失败。EMI时钟源通过优化时钟信号的频谱特性、采用展频技术(SSC)或特殊滤波设计,将电磁能量分散到更宽的频带上,从而显著降低峰值辐射强度,确保系统在复杂的电磁环境中稳定可靠。

EMI时钟源的技术核心

- 展频技术(Spread Spectrum Clocking, SSC):这是最常用的EMI抑制方法。它通过轻微且周期性地调制时钟频率(通常在±0.25%到±2%之间),将原本集中在单一频率的电磁能量“摊薄”到一个窄带范围内,从而降低峰值辐射,满足FCC、CE等电磁兼容性标准。

- 低抖动设计:在抑制EMI的必须保证时钟信号的时序精度(低抖动),否则会影响高速接口(如PCIe, USB, SATA)和数据传输的可靠性。先进的EMI时钟源实现了抑制干扰与保持信号完整性的平衡。

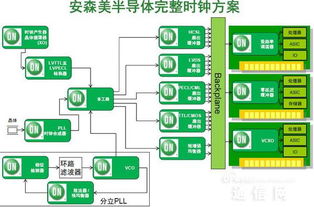

- 多输出与可编程性:现代系统芯片(SoC)和FPGA需要多个不同频率的时钟。集成的EMI时钟发生器可以提供多个低EMI输出,并支持软件配置,极大简化了硬件设计。

最新技术报道与趋势

随着5G通信、人工智能、物联网和汽车电子的飞速发展,对EMI时钟源的性能要求日益严苛,其最新发展呈现出以下趋势:

- 更高频率与更低相位噪声:为支持PCIe 5.0/6.0、DDR5等超高速接口,时钟源的工作频率不断提升,同时对相位噪声(抖动)的控制要求达到飞秒级。新一代产品在提供高达1GHz以上输出频率的保持了卓越的EMI抑制能力。

- 集成与系统级解决方案:时钟源不再是一个独立元件。它正被集成到更大的电源管理芯片(PMIC)或专用时钟芯片组中,提供从核心CPU时钟到外设接口时钟的全套、同步的低EMI解决方案,助力设备小型化。

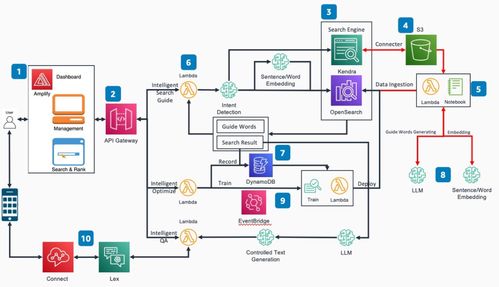

- 软件定义与智能管理:在计算机软件技术服务领域,时钟的配置与管理变得愈发重要。通过I2C、SPI等总线,软件可以动态调整时钟频率、启用/禁用展频功能,甚至根据系统负载和温度进行实时优化,实现性能与功耗、EMI的最佳平衡。这为服务器、数据中心和边缘计算设备提供了灵活的运维手段。

- 汽车级与工业级可靠性:自动驾驶和工业4.0推动了对AEC-Q100(汽车级)和宽温、高可靠性时钟源的需求。这些时钟源能够在极端环境和严苛的EMC标准下稳定工作。

- 主动EMI滤波技术:除了传统的展频技术,一些前沿设计开始采用有源滤波电路,实时监测并抵消特定频段的噪声,提供了更精准的EMI抑制效果。

对计算机软件技术服务的意义

对于软件技术服务工程师和系统架构师而言,理解EMI时钟源至关重要:

- 系统稳定性保障:在驱动开发、系统部署和故障排查时,需知晓时钟配置对系统稳定性的影响。不当的时钟设置可能导致难以复现的间歇性错误。

- 性能调优工具:通过软件接口对时钟进行精细控制,成为系统性能调优(如超频、节能)和满足特定应用场景需求的有效手段。

- 预合规设计支持:在产品的软件层面提前规划时钟管理策略,有助于硬件一次性通过EMC测试,缩短研发周期。

EMI时钟源是连接高性能硬件与稳健软件服务的基石技术之一。随着技术演进,它正朝着更高性能、更智能集成、更紧密的软硬件协同方向发展,持续为数字世界的可靠运行提供着清澈而稳定的“心跳”。